Die Homebrew CPU

Inspiriert durch die „8 bit CPU from scratch“ von Ben Eater hatte ich den Wunsch, ähnliches zu bauen. Dabei wollte ich das Projekt nicht auf dem Breadboard verwirklichen sondern lieber eine schöne Platine zum löten erstellen.

Außerdem sollte der Adressbus 12 Bit breit sein und ein Speicher (ROM oder RAM oder beides) von maximal 4 Kilobyte zur Verfügung stehen. Außerdem wollte ich eine 8 Bit ALU implementieren. Alle Funktionen sollten auch mit LED’s sichtbar gemacht werden.

Bereits am 18.10.2020 begann ich damit, eine entsprechende Schaltung zu entwerfen. Noch am gleichen Tag war die erste Version fertig gestellt und ich bestellte entsprechende Platinen, die am 28.10. eintrafen. Die erste Version war ein vollkommener Reinfall, jede menge Fehler im Design. Einige Teile, wie zum Beispiel die Register funktionierten aber dennoch. Das war zumindest ermutigend.

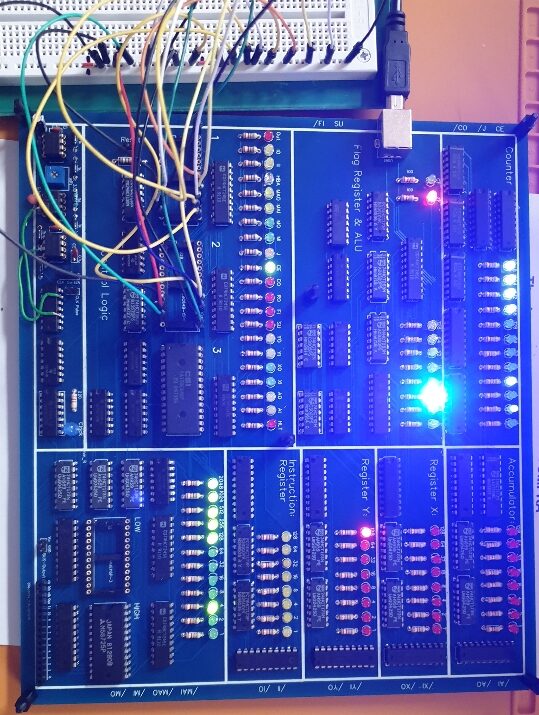

In Betrieb genommen sah das Ganze aber dennoch bunt und durchaus beeindruckend aus:

Es wurde also eine zweite Version fällig. In der zweiten Version waren natürlich viele Fehler behoben und neue Fehler tauchten auf. Zu allem Überfluss vertauschte ich auf der Platine noch zwei Gatter, was natürlich zu sehr schwer nachzuvollziehenden Fehlern führte. Bei den Tests fiel dann noch auf, das die ALU nicht ganz richtig funktioniert. Das Adressregister wollte auch nicht so recht.

Der neue Aufbau war im übrigen zum Teil mit SMD Bauteilen aufgebaut. Alle LED’s und deren Vorwiderstände. Ich habe alles von Hand mit einem kleinen Lötkolben, einer Pinzette und einer Lupe gelötet. Das war anstrengend und war am Ende auch nicht besser. 🙂

Für Version 2 hatte ich bereits einen Teil des Mikrocodes erstellt. Dieser definiert sozusagen die „Befehle“, die die CPU ausführen kann. Frühe Prozessoren funktionierten auch nach diesem Prinzip.

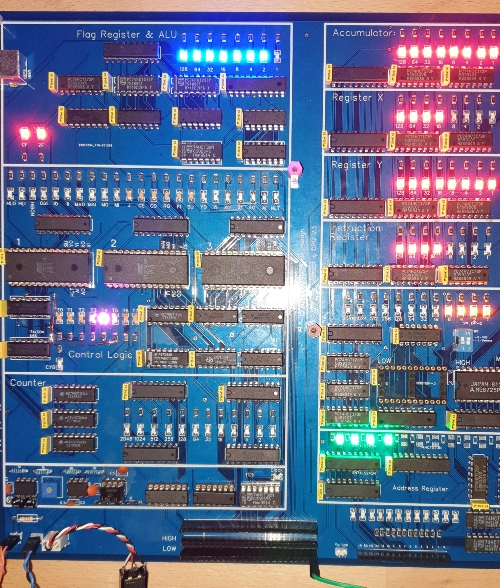

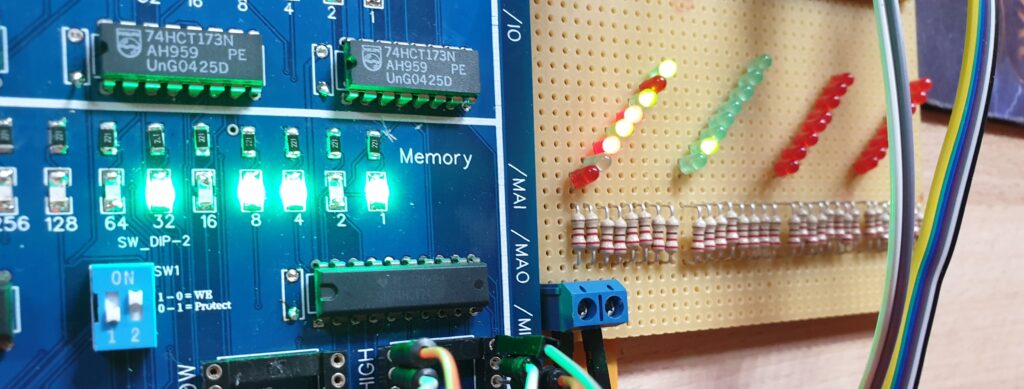

So sah die zweite Version aus (Natürlich wieder beeindruckend leuchtend):

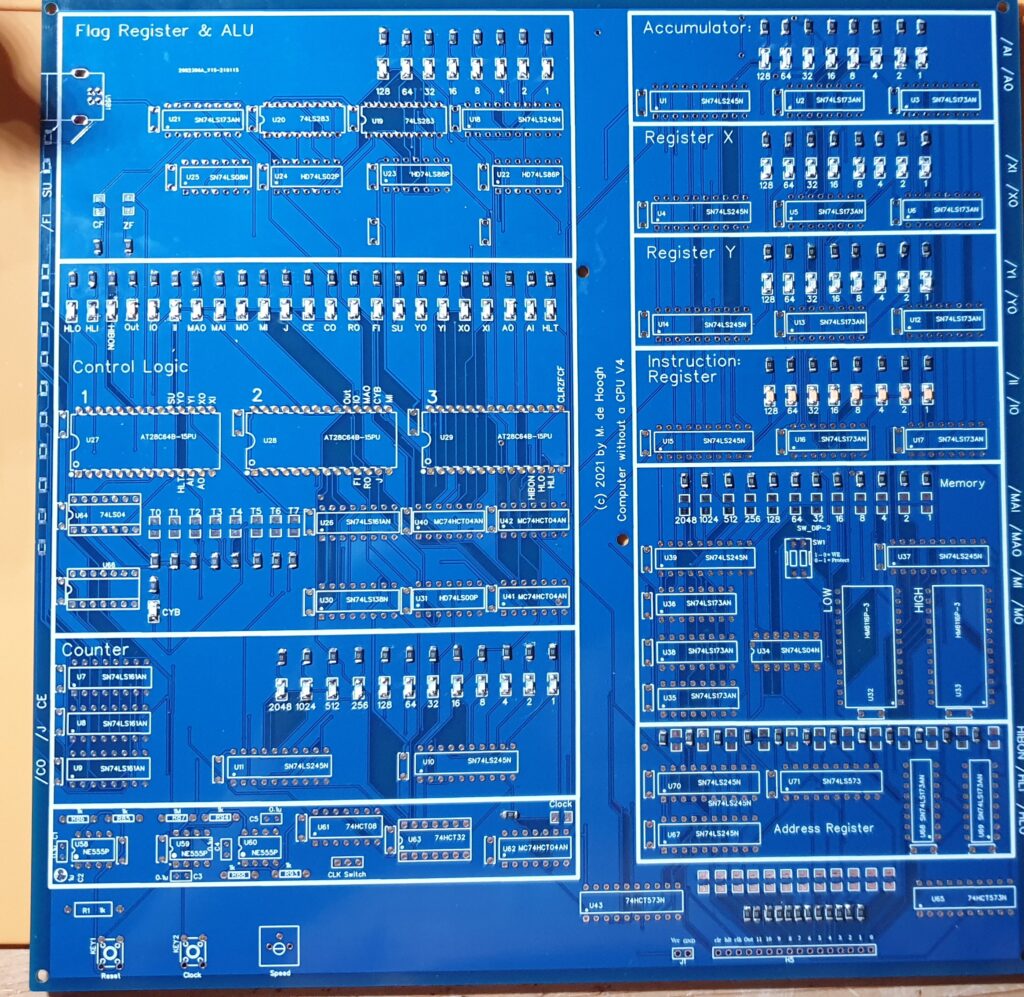

Tja, es musste also eine dritte Version entstehen. Schaltplan überarbeitet: ALU korrigiert, Adresszähler korrigiert, Steuersignale neu verteilt (Einige davon aus dem Mikrocode in den Schaltplan verlegt), Taktgeber korrigiert, Verzicht auf Bustreiber für die LED’s um Platz auf der Platine zu schaffen und ehrlich gesagt auch aus Kostengründen.

Die erforderlichen Platinen wurden bestellt und trafen am 27.01.2021 ein. Nun ist wieder löten angesagt:

Die Lötarbeiten haben wieder einige Stunden in Anspruch genommen. Dabei sind mir leider auch ein paar SMD LED’s kaputt gegangen, die ich dann ersetzen musste. Das war ein wenig tricky. Sie wollten sich nicht so richtig lösen. Unten rechts auf der Platine löste sich sogar eine Leiterbahn von der Platine

05.02.2021.

Zwischenzeitlich war die komplette Platine aufgebaut und diverse Tests hatten begonnen. Bei den Tests fand ich zunächst noch eine fehlende Verbindung, die ich mit einer kurzen Kabel manuell erstellt habe. Bei den Tests stellt sich heraus, dass ich im Design einen Denkfehler hatte. Ich hatte drei Steuersignale (Counter out [CO], Counter Enable [CE] und Memory Address In [MAI] zusammengelegt um so Takte zu sparen bzw. für umfangreichere Befehle mehr Platz in einem Zyklus zu haben.

Das war ein großer Fehler, da diese Signale in vielen Fällen auch getrennt vorkommen können. Ich musste deshalb auf das Signal Cycle Break [CYB], welches einen Prozessorzyklus bei kurzen Befehlen vorzeitig beenden konnte, verzichten, um die drei genannten Signale wieder trennen zu können. Mit einigen Lötbrücken und durchtrennten Leiterbahnen war es mir möglich. Der Preis ist allerdings eine erheblich langsamere Verarbeitung, da jetzt immer 8 Takte für einen Befehl durchlaufen werden, obwohl weniger erforderlich wären.

Nunja… Weiter mit den Tests. Als nächstes stellt ich fest, dass die Memory-Einheit nicht funktioniert. Die Daten (Das Programm), welche sich im EEProm befinden, erscheinen nicht auf dem Bus…..

Da musste ich erst einmal verdauen und quittierte mit einer Pause…

13.03.2021 / 14.03.2021:

Weitere Tests liefen an. Jetzt intensives Messen der Signale am Sockel des EEProm. Chip Enable der Bausteins wird ordentlich an den Chip gelegt. Output Enable kommt auch an. Die Addresse wird ebenfalls korrekt an das EEProm angelegt…. Write Enable des EEProm liegt auf High-Pegel. Trotzdem kommen keine Informationen aus dem Speicher auf den Datenleitungen an. Zunächst wieder mal keine Ahnung, warum das so ist.

Ich schaute mir noch einmal meinen Schaltplan an und staune: An meinem EEprom (und auch am parallel liegenden SRAM) fehlen die Anschlüsse für Pin 22 und Pin 19 (A9 und A10). Diese heißen im Plan stattdessen genauso wie I0 und I1 (die ersten beiden Bits des Datenbusses). Pin 22 hieß 9, I0 ebenfalls, Pin 19 hieß 10, I1 ebenfalls. Das Symbol des Bausteins HM6116P, welches ich als Footprint für das EEProm und das SRAM verwendet habe, ist fehlerhaft.

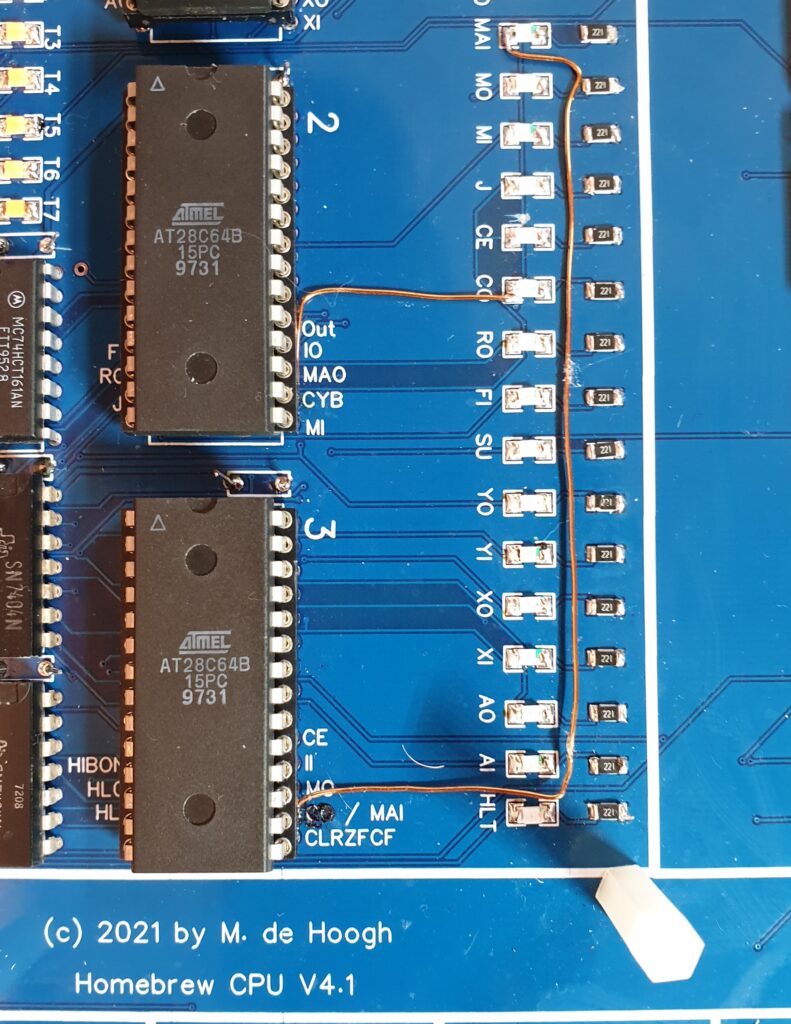

Hatte ich das Symbol entworfen?? Ich erinnere mich nicht!! Die Folge war jedenfalls, dass Die Adressleitung A9 mit dem Datenbit 0 und die Adressleitung A10 mit dem Datenbit 1 verbunden war. Das zu korrigieren (Die passenden Punkte auf der Leiterplatte für die Reparatur zu finden, Leiterbahnen zu durchtrennen und neue Verbindungen zu schaffen) hat mich 3 Stunden gekostet.

Nachdem das endlich korrigiert war, musste ich erneut testen. Das ernüchternde Ergebnis: Es funktioniert weiterhin nicht!!

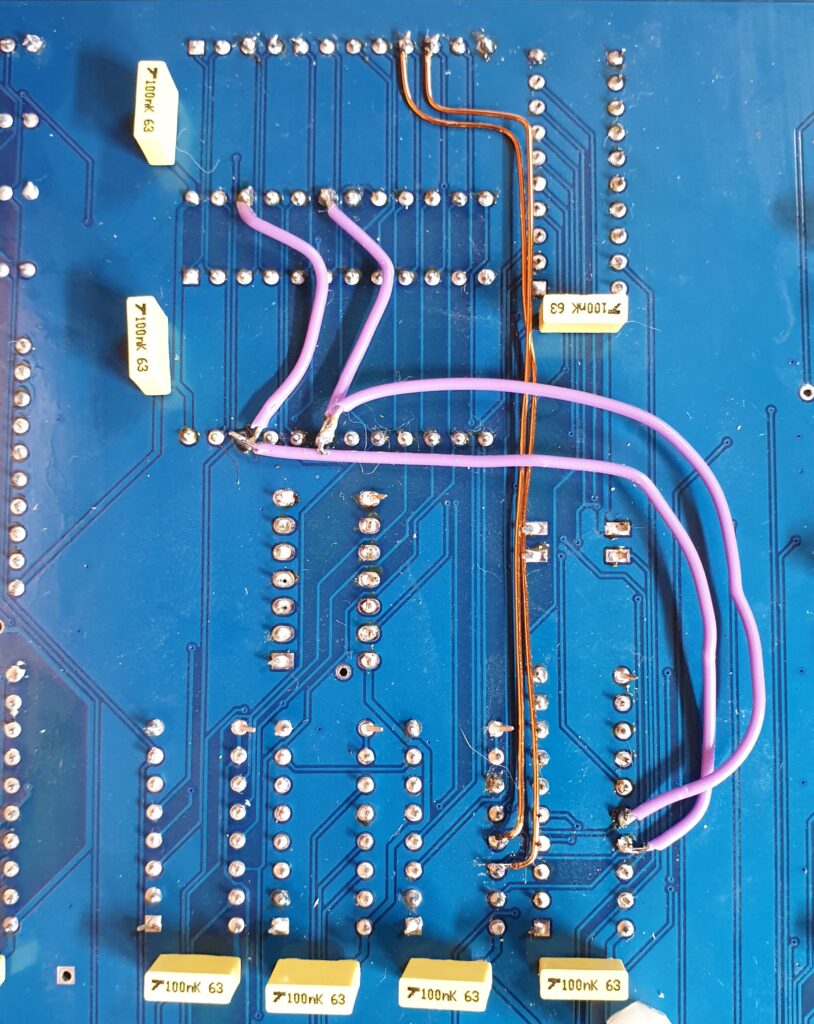

Links die professionelle Korrektur der fehlerhaften Adress- und Datenleitungen. Oben Ein Signaltest am Sockel des SRAM-Bausteins. Adresse, Output Enable und Daten werden per LED angezeigt.

19.06.2021 – 25.08.2021:

Die Summe der Fehler aus der Version vom 13.03.2021 war am Ende zu groß und sie mit der Trennung von Leiterbahnen und das Verlegen von Ersatzleitungen erwies sich am Ende zu aufwändig. Also habe ich den korrigierten Schaltplan am 14.06.2021 erneut als PCB bestellt. Der Versand durch JLCPCB erfolgte am 19.06.2021. Wann die Platinen genau angekommen sind, weiß ich nicht mehr genau. Es ging aber sehr schnell.

Die neuen PCB’s wollten sogleich bestückt werden. Parallel zur PCB-Bestellung hatte ich die passenden Bauteile bestellt. Es sind ja doch so einige erforderlich. Die EEProms und den RAM-Baustein waren immer gesockelt und können auch weiter genutzt werden. Alle anderen Bauteile hatte ich ohne Sockel bestückt. Diese waren in den Vorgängerversionen dann verloren.

Die ersten Tests der neuen Platine waren durchaus vielversprechend. Allerdings habe ich nur kurz ein paar Kleinigkeiten getestet und dann eine kleine „Sommerpause“ eingelegt.

Ab dem 16.08.2021 gingen die echten Tests los. Es hat sich herausgestellt, dass der Mikrocode ein paar Fehler enthielt. Diese zu korrigieren war nicht ganz leicht, da seit dem Beginn des Projekts doch einiges an Zeit verstrichen war. Ansonsten konnten die „Maschinenbefehle“ aber mit Drahtbrücken statt dem EEProm mit dem Programm simuliert werden. Und die Ergebnisse dieser Tests sahen ebenfalls positiv aus.

Also musste ein kleines Programm der einzelnen Maschinenbefehle her, um alle Befehle und den Mikrocode einmal zu testen. Komischerweise hat das überhaupt nicht funktioniert. Aus dem EEProm kam über den Datenbus selten raus, was eigentlich drin war. Nichts hat funktioniert. Nach langen Tests und dem Wissen, dass mit Drahtbrücken statt EEProm alle Befehle so funktioniert haben, wie es der Mikrocode vorgesehen hatte, hatte ich den Verdacht, dass die Ausgangssignale des EEProm zu schwach sein könnten, um die Elektronik drumherum (Datenbus, SMD-LED’s) zu treiben.

Am 21.08.2021 entwickelte ich deshalb eine kleine Huckepackplatine für den EEProm-Sockel auf dem neben einem Sockel für das EEProm zusätzlich ein Latch (74HCT573) sitzt, welches die Ausgangssignale verstärkt. Das Prinzip funktioniert zwar grundsätzlich, aber eben nicht vollständig. An dem Punkt habe ich das Projekt wieder zur Seite gelegt, da ich nicht in der Lage bin, das Problem auf Anhieb zu beseitigen.

Es wird also eine weitere Test- und Korrekturrunde geben….